QUartUs PRIMEでniosⅡ DE10-lite編

はじめに

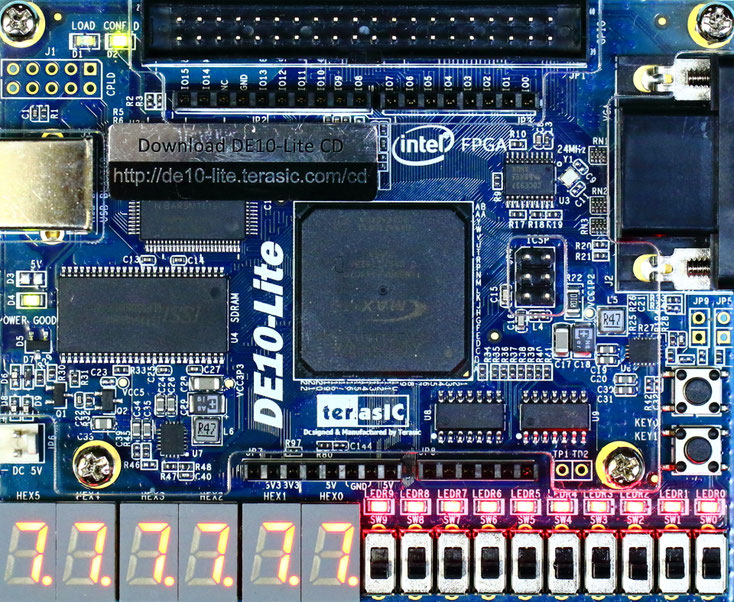

Intel社(旧アルテラ)のFPGA用プロセッサ(NiosⅡ)の設計手順をFPGA評価ボードのDE10-lite(Terasic社)を題材に

紹介します.ここではツールの導入とハードウェアとソフトウエアの作成手順を紹介します。

〇手ぶらでOK!実習・ゼロから始めるZynq SoC開発「超」入門

初心者大歓迎!ハード,ソフトのいいとこどり開発に挑戦

2024年5月11日(土) CQ出版社セミナルーム

1.ツールの準備

1-1.インストール情報

Quartus Primeがインストール済みの場合は"2.新規プロジェクトの作成"へお進みください.

Quartus Primeライト・エディションはintel社FPGAの一部を無償で設計できるFPGA開発ツールです。

インストール手順はintel社の以下の資料(インテル® Quartus® Prime開発ソフトウェア ダウンロード & インスト-ル クイック・スタート・ガイド )を参考にしてください。

http://dl.altera.com/static/quick_start_guide/quick_start_guide_17.0_ja.pdf

1-2.ダウンロードとインストール

intel社の以下サイトからQuartus Primeをダウンロードします。

http://dl.altera.com/?edition=lite

クイック・スタート・ガイドを参考にしてインストールしてくださ。

2.新規プロジェクトの作成

2-5.ファイル追加

追加せずに

Nextをクリック

2-6.デバイス指定

デバイスファミリ、package等を指定してデバイスを絞り込み

DE10-liteのデバイスに合わせて10M50DAF484C7Gを指定する。

Nextをクリック

3.ハードウエアの設計

3-1.Qsysの起動

NiosⅡプロセッサを含む回路はQsys(Platform Designer)で作成します。

Quarts PrimeのメニューからTools->Qsys(Platform Designer)を選択

※QsysはPlatform Designerに名称が変更になりました。

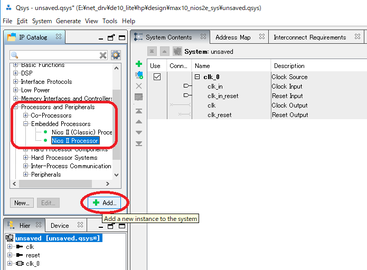

3-2.NiosⅡの追加

起動したQsys(Platform

Designer)のIP catalogで

Prcessors and Peripheralsy->Embedded Processors->NiosⅡProcessor

を選択して"+Add.."をクリックしてNiosⅡを追加する

3-4.NiosⅡの接続

Qsys(Platform

Designer)のSystem

Cntentsで

nios2_gen2_0のclkとclk_0のclkの接点をクリックして接続する。

nios2_gen2_0のresetとclk_0のclk_resetの接点を

クリックして接続する。

3-5.On Chip Memoryの追加

起動したQsys(Platform

Designer)のIP

catalogで

Bsic Functions->On Chip Memory->On Chip Memory(RAM or ROM)

を選択して"+Add.."をクリックしてNiosⅡを追加する

3-7.On Chip Memoryの接続

Qsys(Platform

Designer)のSystem

Cntentsでonchip_memory2_0のclk1とclkとclk_0のclkの接点を

クリックして接続する。

onchip_memory2_0のreset1とclk_0のclk_resetの接点を

クリックして接続する。

onchip_memory2_0のs1とnios2_gen2_0のdata masterの接点をクリックして接続する。

onchip_memory2_0のs1とnios2_gen2_0のinstruction masterの接点をクリックして接続する。

3-8.On Chip Memoryのアドレス設定

Address Mapでonchip_memory2_0.s1のnios2_gen2_0.data_masterの設定の

開始アドレスを0x0001_0000に変更

Address Mapでonchip_memory2_0.s1のnios2_gen2_0.instruction_masterの設定の

開始アドレスを0x0001_0000に変更

3-9.NiosⅡのメモリ設定の変更

System Cntentsでnios2_gen2_0をクックして

parametrsのVectorタグで

Reset vector memoryをonchip_memory2_0.s1に設定

Exception vector memoryをonchip_memory2_0.s1に設定

3-10.System ID Peripheralの追加

起動したQsys(Platform

Designer)のIP

catalogで

Bsic Functions->Simulation Debug and Verification->Debug and Performance->System ID Peripheral

を選択して"+Add.."をクリックしてNiosⅡを追加する

3-12.System ID Peripheralの接続

Qsys(Platform

Designer)のSystem

Cntentsで

sysid_qsys_0のclkとclkとclk_0のclkの接点をクリックして接続する。

sysid_qsys_0のresetとclk_0のclk_resetの接点を

クリックして接続する。

sysid_qsys_0のcontrol_slaveとnios2_gen2_0のdata masterの接点をクリックして接続する。

3-13.JTAG_UARTの追加

起動したQsys(Platform

Designer)のIP

catalogで

Interface Protocols->Serial->JTAG UART

を選択して"+Add.."をクリックしてNiosⅡを追加する

3-15.JTAG_UARTの接続

Qsys(Platform

Designer)のSystem

Cntentsで

jtag_uart_0のclkとclkとclk_0のclkの接点をクリックして接続する。

jtag_uart_0のresetとclk_0のclk_resetの接点を

クリックして接続する。

jtag_uart_0のavalon_jtag_slaveとnios2_gen2_0のdata masterの接点をクリックして接続する。

jtag_uart_0のirqとnios2_gen2_0のirgの接点をクリックして接続する。

3-16.System ID PeripheralとJTAG_UARTのアドレス設定

Address Mapでsysid_qsys_0.control_slaveのnios2_gen2_0.data_masterの設定の

開始アドレスを0x0002_0000に変更

Address Mapでjtag_uart_0.avalon_jtag_slaveのnios2_gen2_0.data_masterの設定の

開始アドレスを0x0002_0100に変更

3-18.名前を指定して保存

Qsys(Platform

Designer)の終了時にデザインに名前が付けられてない場合は

名前を聞かれる。名前を設定して保存をクリック

この名前はNisⅡを含んだ回路のモジュール名になる。

ここではmax10_nios2eとしました。

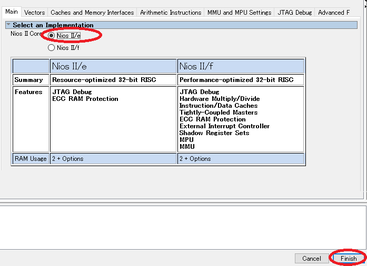

3-22.Generateの完了

Generate Completedウィンドに

Generate Completed successfullyと表示されればモジュール設計データの作成が完了です。

Finishをクリック

3-30.トップ回路記述

エディタでトップ回路をVerilog-HDLで記述して保存

トップ回路はQsysで作成した max10_nios2eをインスタンスしてある

module max10_nios2e_sys (

clk,

reset_n);

input clk;

input reset_n;

max10_nios2e u0 (

.clk_clk (clk), // clk.clk

.reset_reset_n (reset_n) // reset.reset_n

);

endmodule

3-34.デバイスオプションの設定③

ConfigurationのConfiguration Modeで

Single Compressed Image with Memory Intialization(512Kbits UFM)

を選択してOKをクリック

3-37.ピン配置指定

Pin Plannerで

clkのlocationをPIN_P11、I/OStandardを3.3V LVTTLに指定

reset_nのlocationをPIN_B8、I/OStandardを3.3V LVTTLに指定

指定後にPin Plannerを閉じる

3-39.Programmerの起動

Compile Designに緑いろのチェックが付けば

コンパイル完了

De10-liteをPCのUSBポートに接続する

初回の接続ではドライバがインストールされる。

Quartus PrimeのメニューからTools->Programmerをクリック

3_41.プログラミングファイルの指定

max10_nos2e_sys.sofを指定して

Openをクリック

3_42.プログラミングファイルの書き込み

Program/Cnfgureにチェックを入れる

Startをクリックすると書き込み開始

100%(Successful)

と表示されると書き込み完了

これでハードウェアの準備は完了

4.NiosⅡプロセッサ用プログラムの作成

4_1.NiosⅡ software Build Tools for Eclipseの起動

Quartus PrimeのメニューからTools->NiosⅡ software Build...をクリック

★★★セミナー情報★★★<広告>

〇手ぶらでOK!実習・ゼロから始めるZynq SoC開発「超」入門

初心者大歓迎!ハード,ソフトのいいとこどり開発に挑戦

2024年5月11日(土) CQ出版社セミナルーム